Timing

Products

NAMC-PTM

- Features VCOCXO and VCTCXO

- Detection of internal or external clocking sources

- Quality rating of clocking signals

- Clock I/O at front panel via BNC connectors

- Operation in standard AMC- or dedicated PTM slot (if supported by Backplane)

NAMC-psTimer-RTM

- RF-Trigger connection to RTM backplane

- Programmable delay line

- 3x RJ45 at Rear Panel for differential signal distribution

- 9x Lemo connectors at Rear Panel for single-ended signal distribution

- 3 channels with 5ps solution

NAMC-psTimer

- Trigger synchronization with jitter of approx. 10ps

- Numerous programmable receiver outputs

- 2x trigger / 1x precision clock towards front panel as LVDS signals via RJ45

- Optional mezzanine and RTM for increased number of I/O

- Data word and table distribution via fiber links

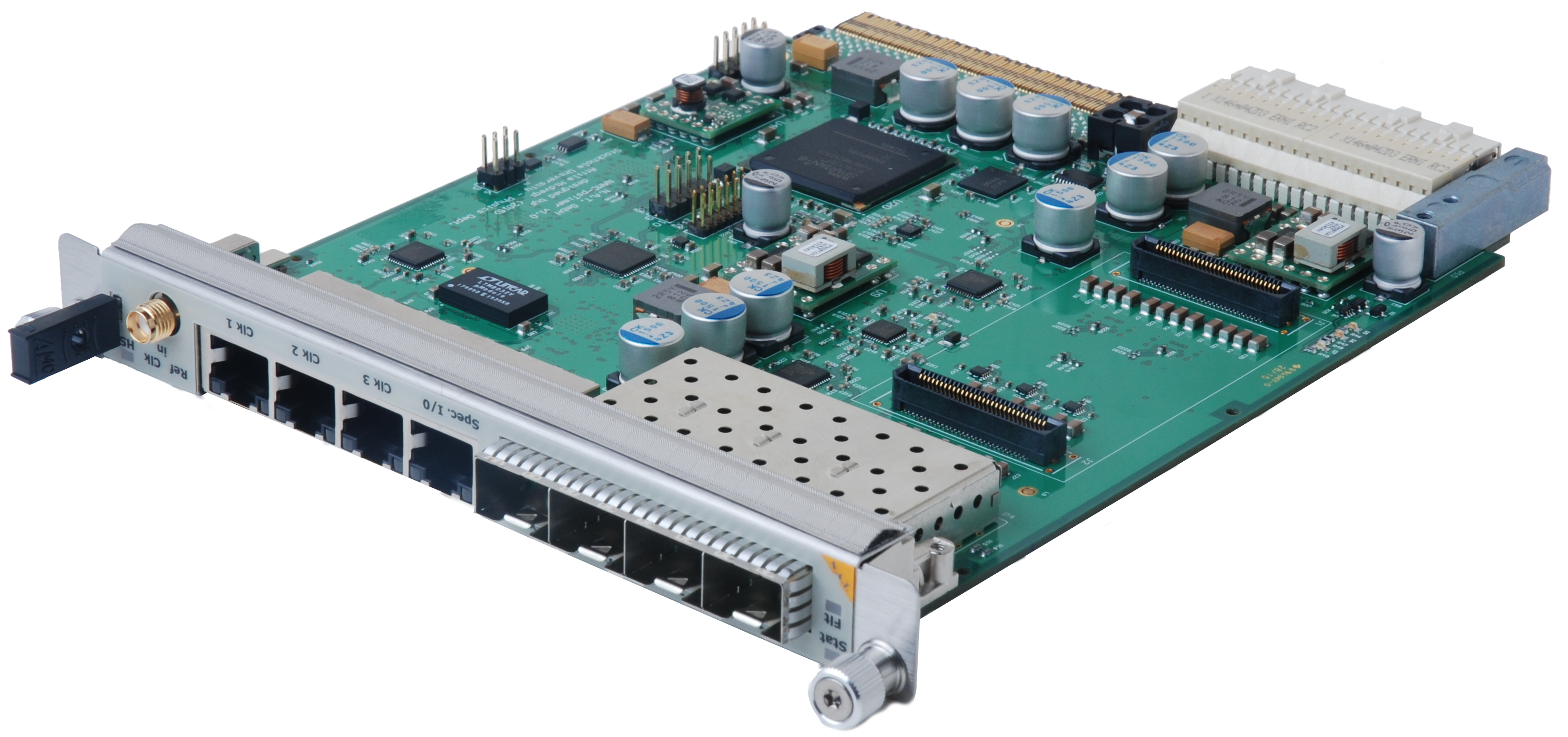

NAT-MCH-PHYS80-Q

- Replacement available:

- NAT-MCH-G4 Family

- Overview

- LTB / LTS apply