FMC/XMC

FMCs and XMCs are both mezzanine cards mounted on a corresponding base board, but with a different field of application.

FPGA Mezzanine Cards are intended to enhance and customize functionality of an FPGA implemented on the base board. These mezzanines offer SerDes functionality as well as flexible and variable I/O to the programmable logic. Thereby, an FMC has no standardized bus structure.

XMCs – also referred to as Switched Mezzanine Cards – are direct derivates of PMCs and support a PCI(e) bus structure. They are designed to support PCI Express or other high speed serial communication in a more robust and smaller cross-platform form factor.

Products

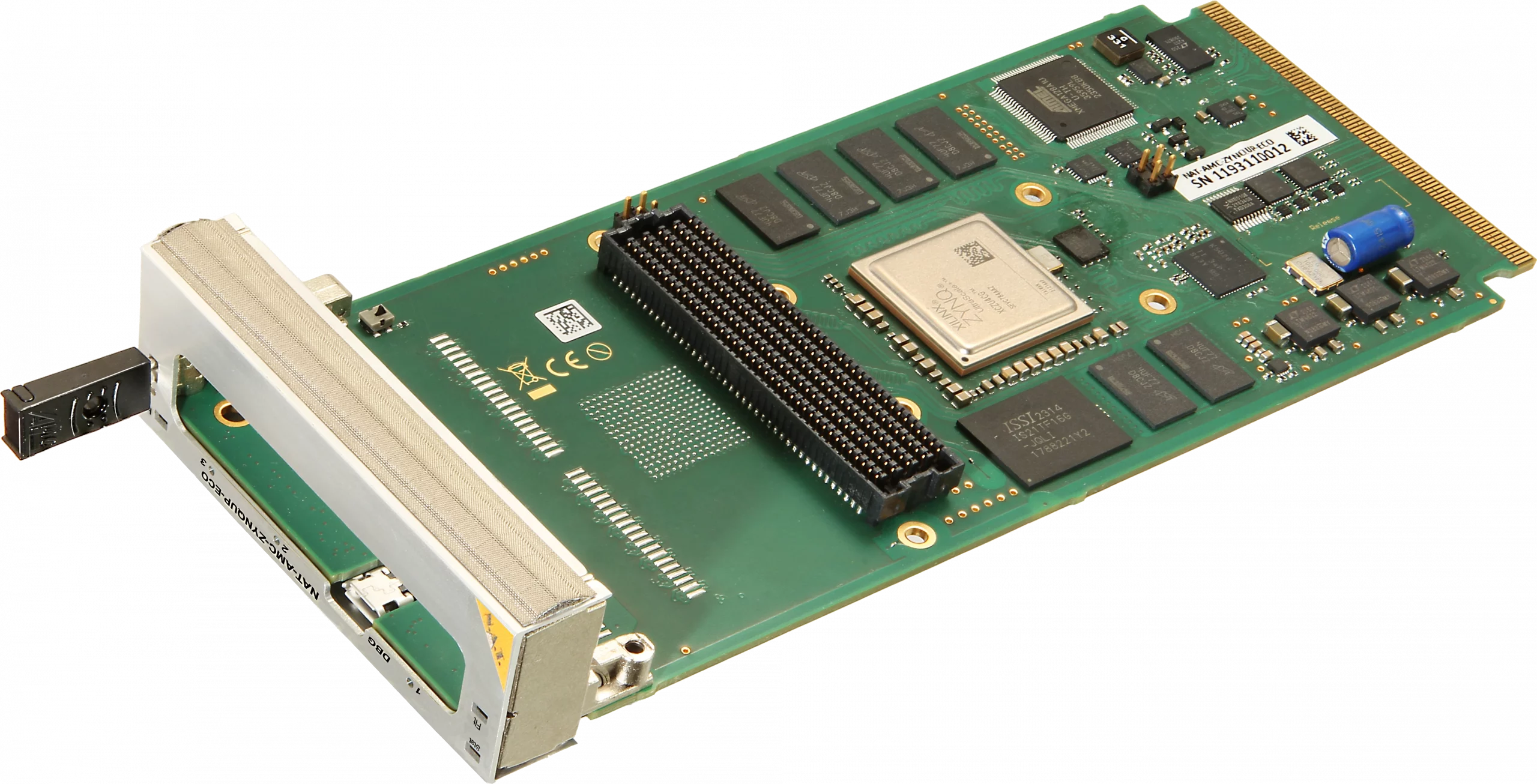

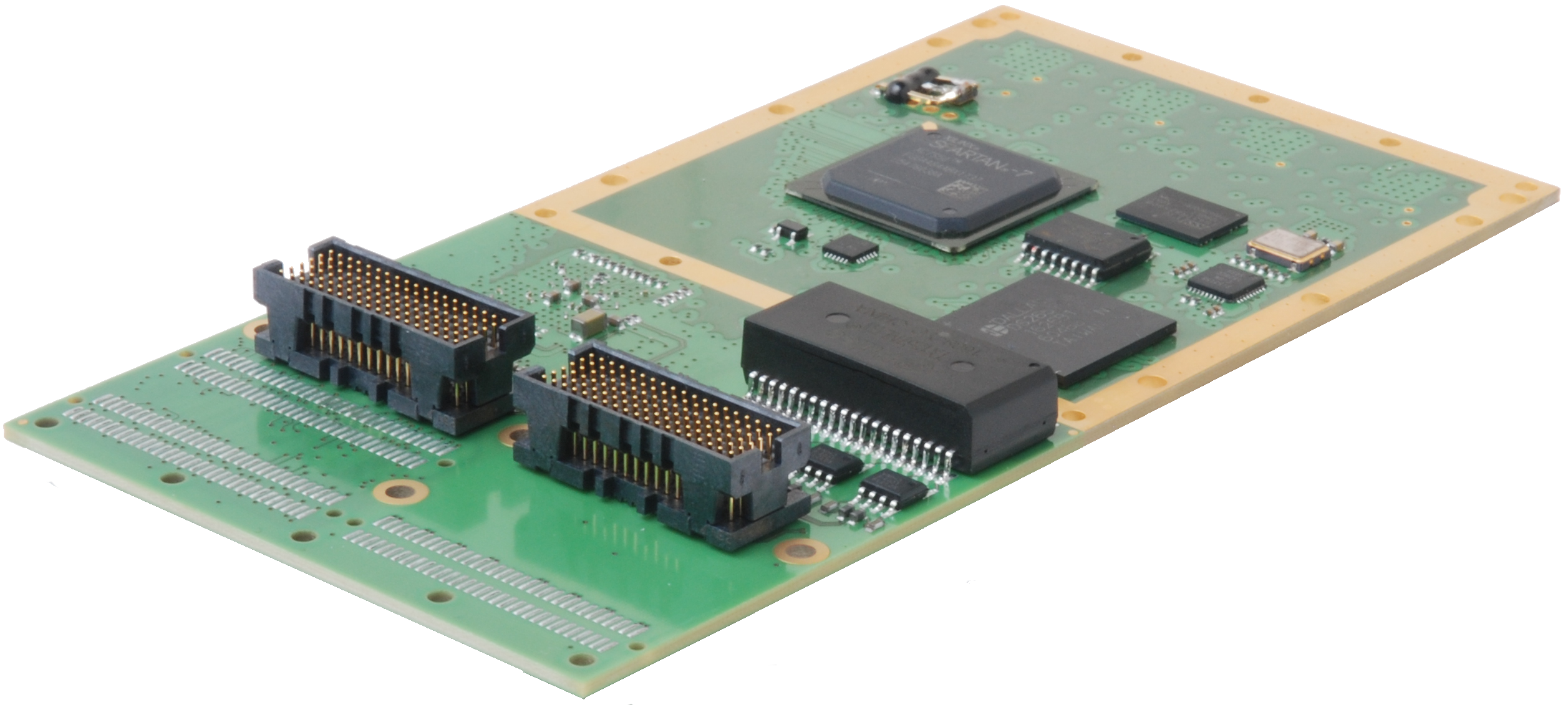

NAT-AMC-ZYNQUP-ECO

- Modern Xilinx ZynqUP FPGA portion for time-critical, massive parallel processing

- Multi-core ARM CPU for higher-level software tasks

- Low Pin Count connectors as defined by VITA 57.1

- Configurable clocking options

NAT-PCIe-XMC-4E1

- Xilinx Spartan-7 XC7S50 FPGA

- Maxim/Dallas DS26518 E1 / T1 framer

- Broadcom/PLX PEX 8112 PCIe-to-PCI bridge

- 64 MB SPI flash and 512 MB DDR3 DRAM

- Standard height, half-length PCI Express x8 add-in card

NAT-XMC-4E1

- Xilinx Spartan-7 XC7S50 FPGA

- Maxim/Dallas DS26518 E1/T1 framer

- Broadcom/PLX PEX 8112 PCIe-to-PCI bridge

- 64 MB SPI flash and 512 MB DDR3 DRAM

- Xilinx Vivado Lab Edition software

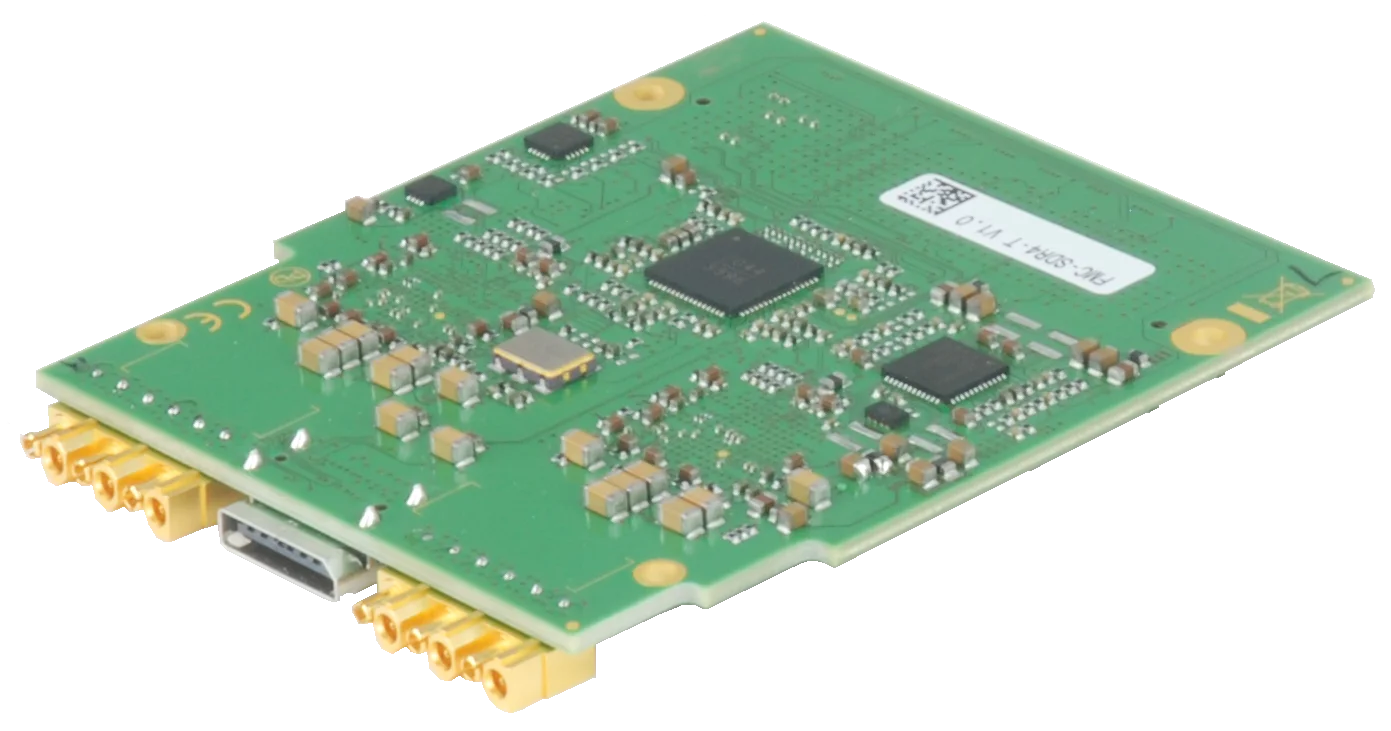

NAT-FMC-SDR4

- 2x Analog Devices ADRV9009 dual RF transmitters, receivers, and observation receivers

- 4x Rx/Tx channels with large bandwidth

- Synchronizable for creating large phased-arrays

- Multiboard synchronization

- VITA 57.1 FMC high pin count (HPC) connector

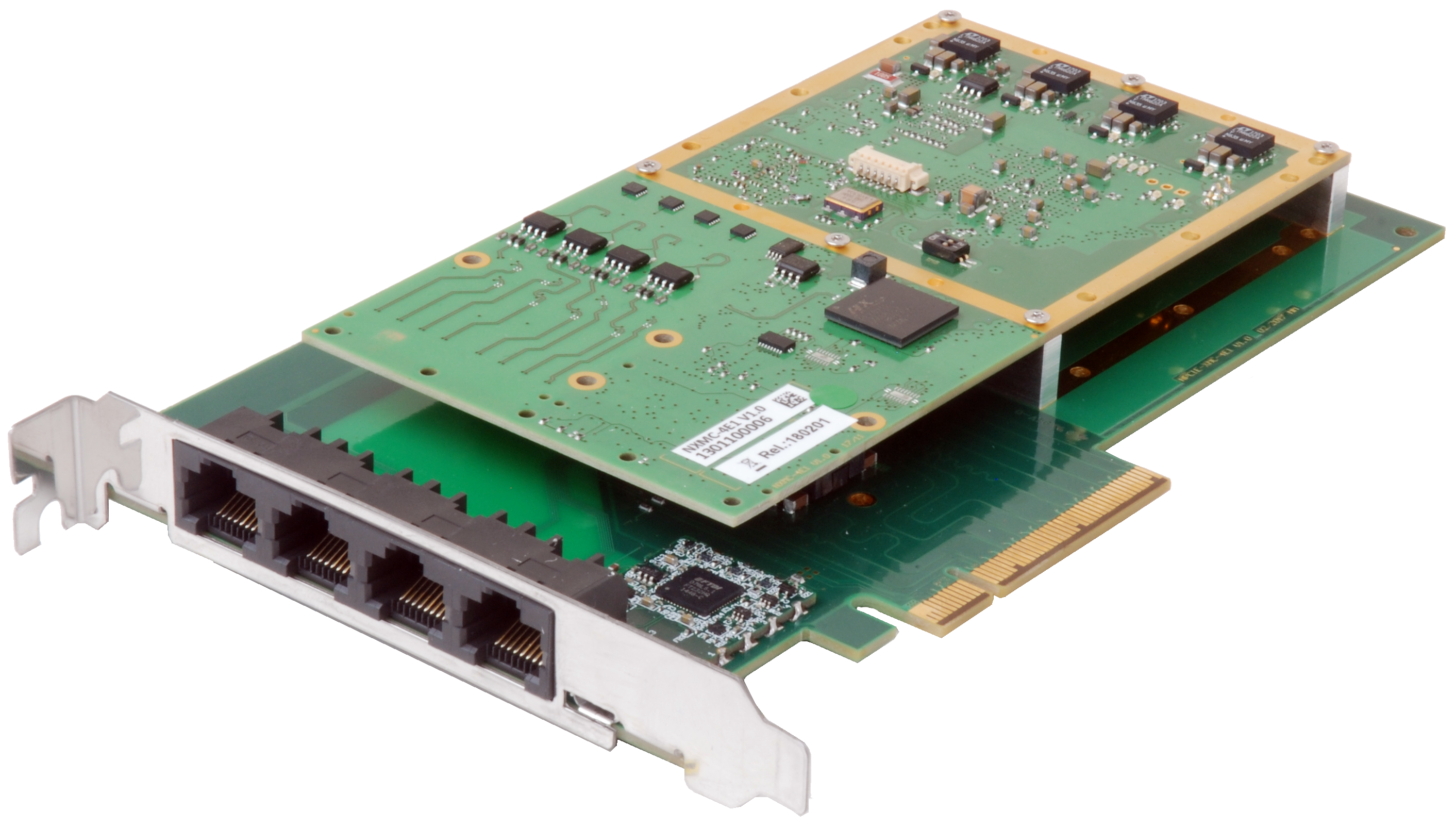

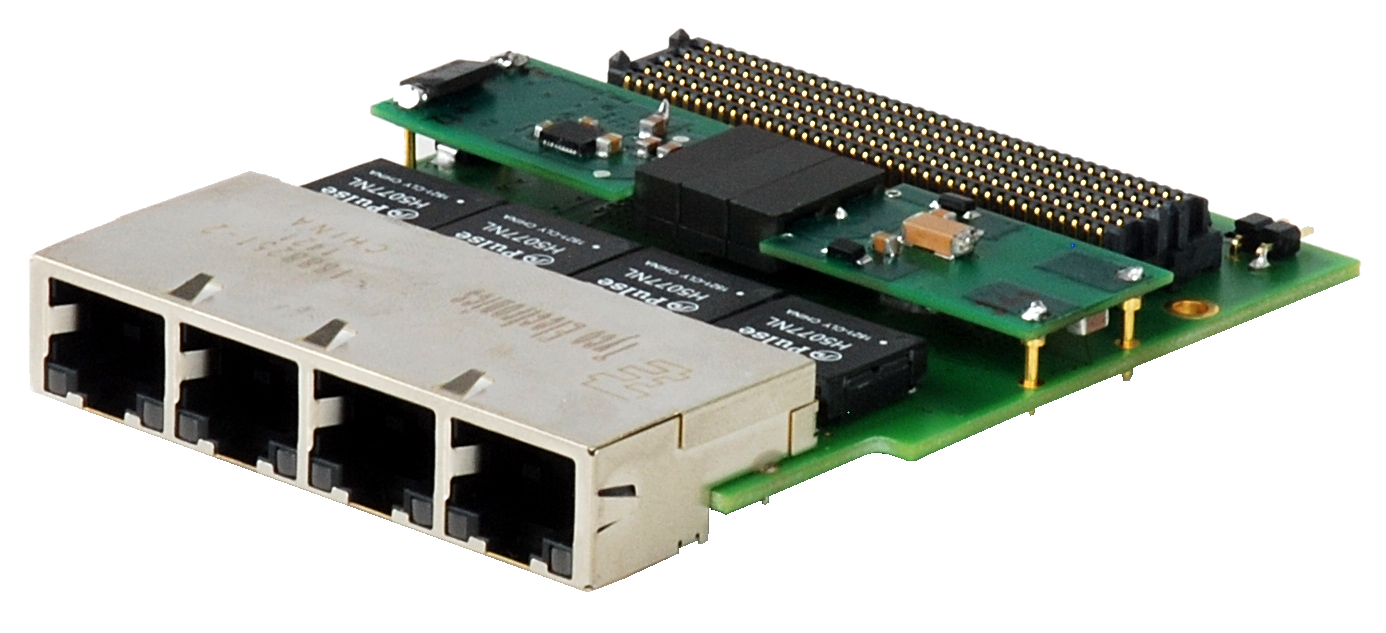

NAT-FMC-PoE

- 4x IEEE 802.3af compatible RJ45 front ports

- High-efficient power conversion

- VITA 57.1 FMC high pin count (HPC) connector

- 4x SGMII and I²C at the FMC connector

NAT-AMC-ZYNQUP-SDR

- Combination of NAT-AMC-ZYNQUP-ADV carrier and 1x or 2x NAT-FMC-SDR mezzanines

- Up to 4x Analog Devices ADRV9009 dual RF transmitters, receivers, and observation receivers

- Xilinx ZynqUP+ FPGA SoC with quad-core ARM Cortex-53 and dual-core Cortex-R5

- Various customizable memory options and numerous interfaces towards front panel and backplane

- Development platform in ready-to-deploy package with optional housing

NAT-AMC-ZYNQUP-ADV

- Quad-core ARM Cortex-A53 (application processing unit)

- Dual-core ARM Cortex-R5 (real-time processing unit)

- Single High Pin Count FMC slot, VITA 57.1 compliant

- Access to FMC front panel interfaces

- Wide range of backplane interconnects

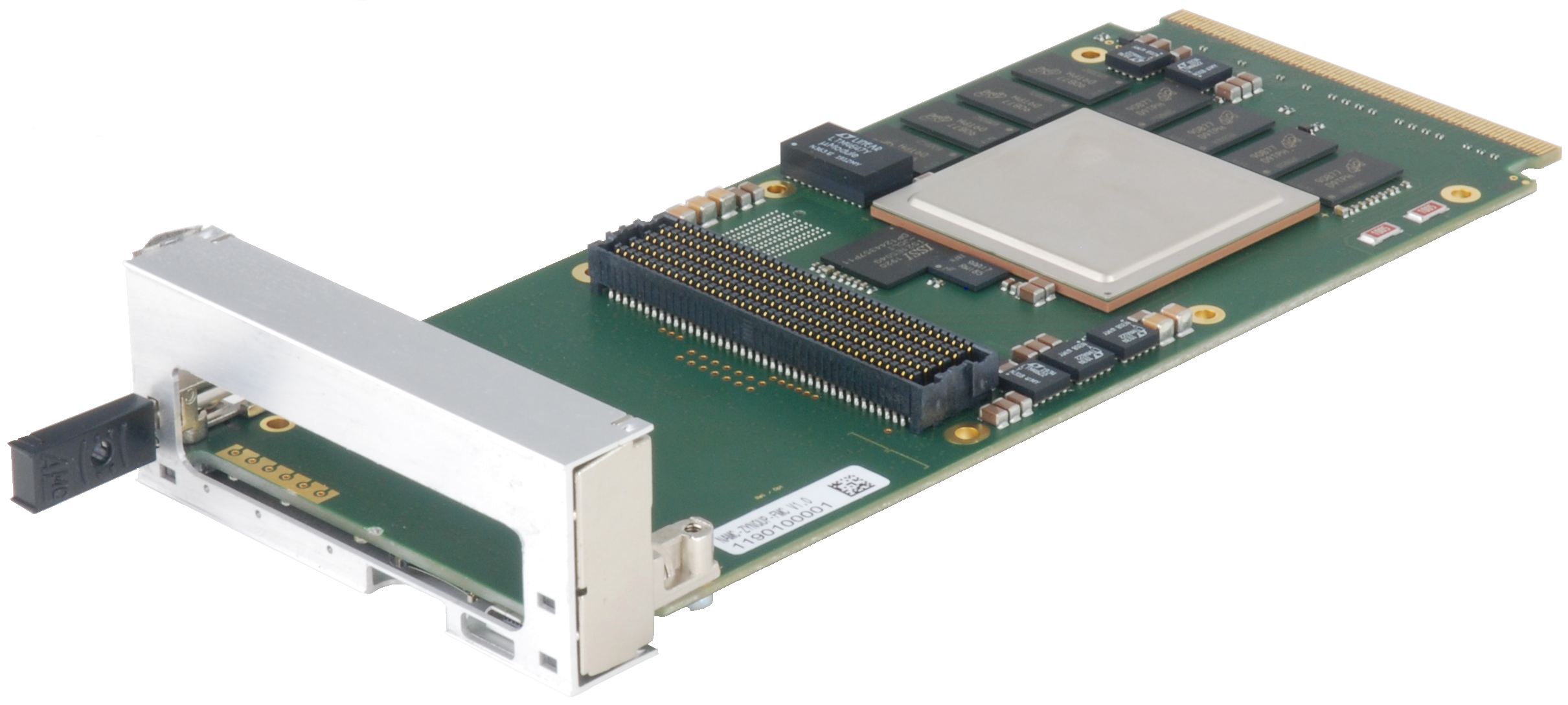

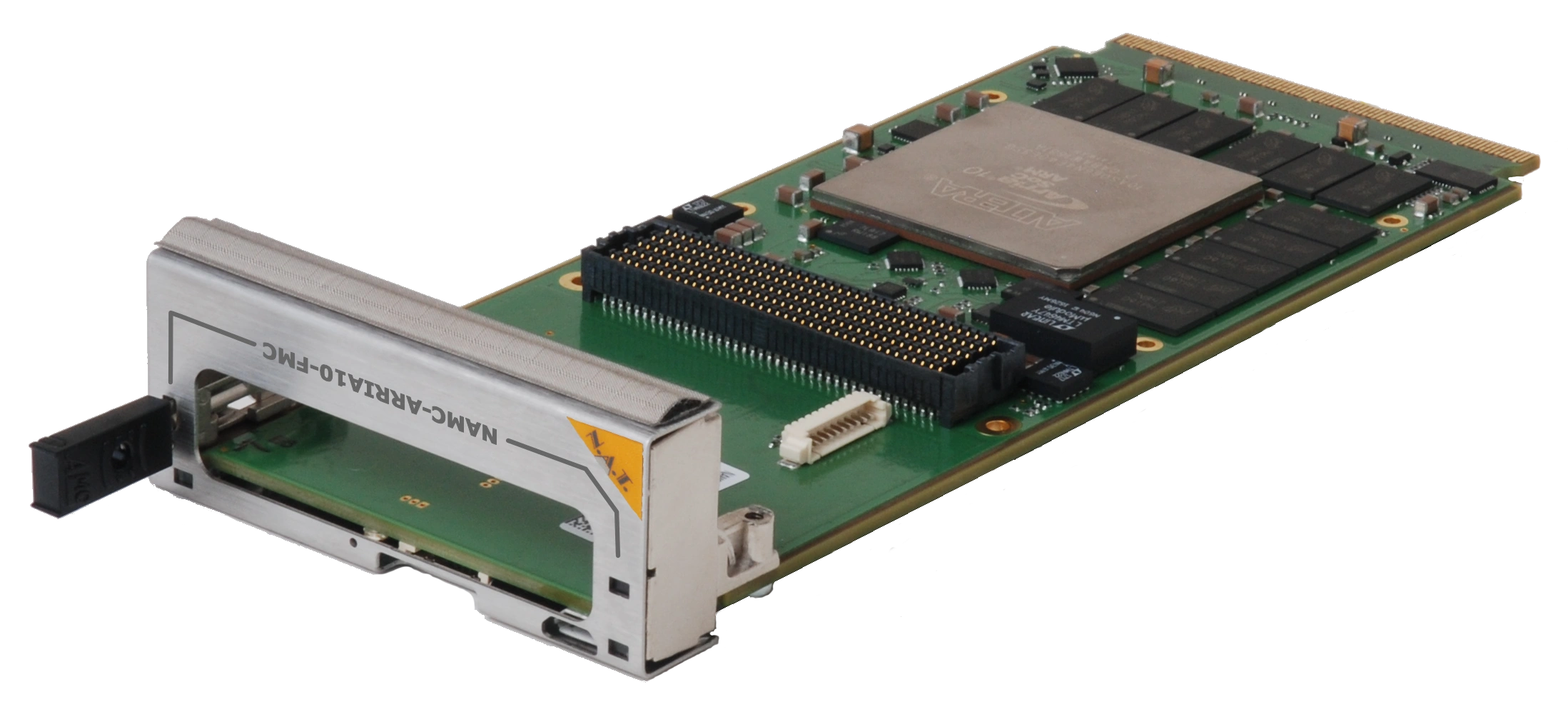

NAT-AMC-ARRIA10-FMC

- Choice of Altera ARRIA 10 GX or SX SoC

- Dual-core ARM Cortex A9

- Single High Pin Count FMC slot, VITA 57.1 compliant

- Access to FMC front panel interfaces

- Wide range of backplane interconnects