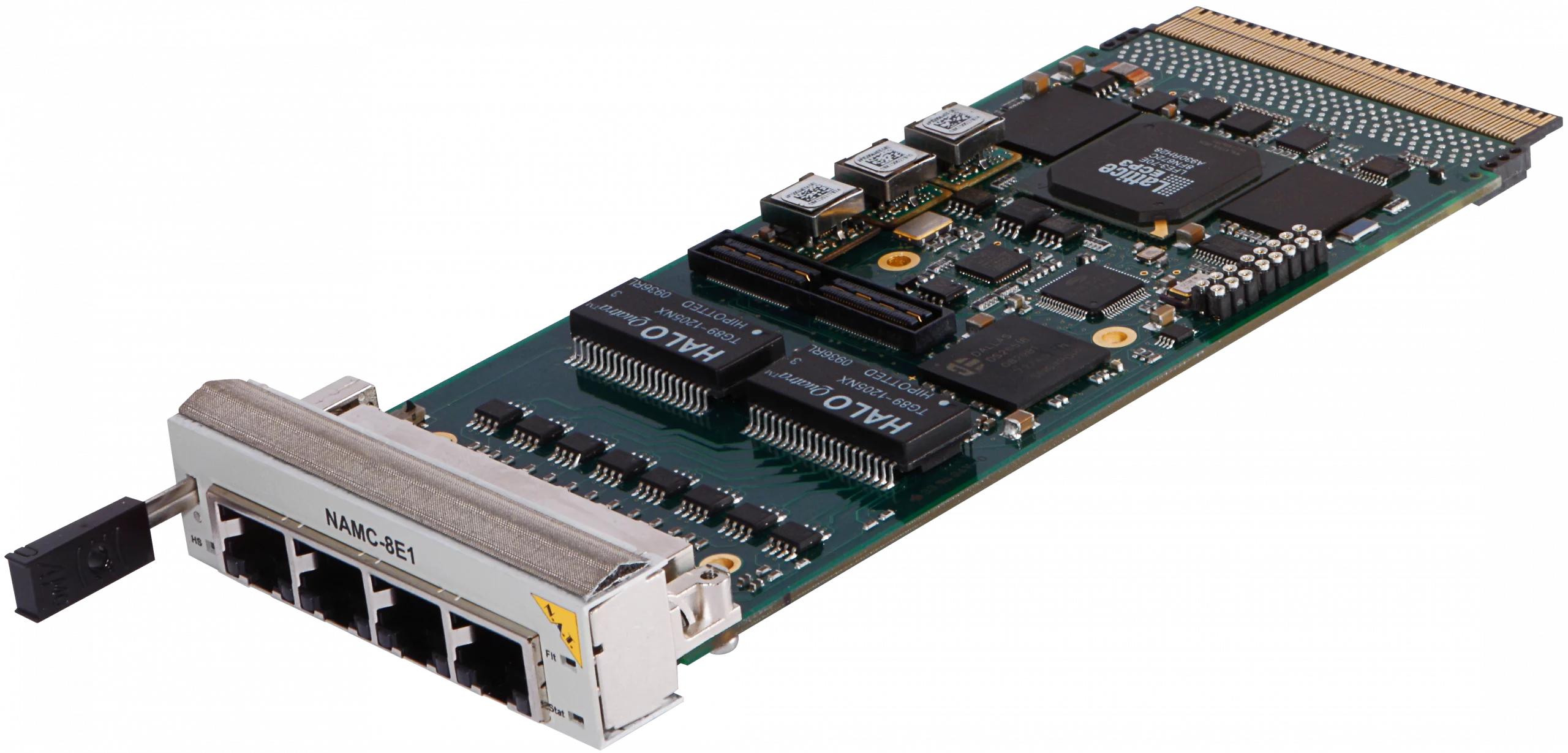

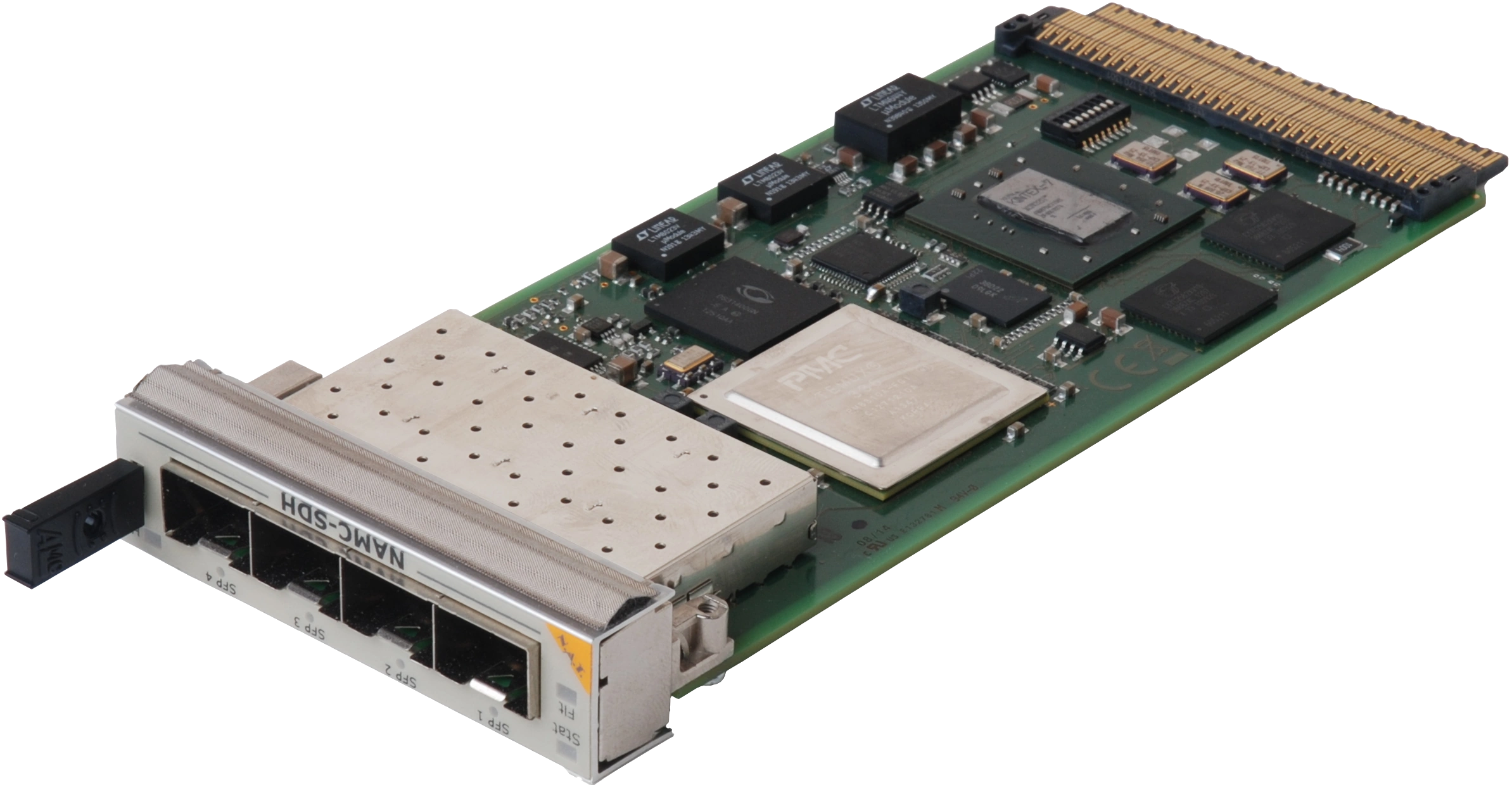

NAT-AMC-SDH

AMC line Interface board for SDH/SONET from/to TDM applications

Description

The NAT-AMC-SDH is a telecommunication interface in AMC form factor, targeting at telecom applications dealing with Synchronous Digital Hierarchy (SDH) in SDH/SONET networks. The NAT-AMC-SDH creates a full interworking interface between STM-1/4 based SDH/SONET and classic TDM based E1/T1 networks.

The add/drop multiplexer/demultiplexer implements 252 E1 or 336 T1 framers, while for seamless interactions between the TDM domain and the Ethernet domain, the NAT-AMC-SDH features a Xilinx Kintex-7 FPGA for time-slot-interchanging (TSI) data pre-processing, manipulation or filtering.

An optional function block for the FPGA implements an HDLC controller, which offers a total capacity of 2000 x 64 kbit/s (2000 x DS0 bandwidth) per direction. It can be configured to handle up to 2000 separate 64 kbit/s channels, or to combine each up to 31 of the 64 kbit/s time-slots to super-channels. The TSI Block is used to either cross-connect a time-slot directly from Rx to Tx, to connect a time-slot to the ITDM controller, or to connect one or multiple of them to a channel of the HDLC controller.

The NAT-AMC-SDH provides four optical interfaces on the front panel represented by four SFP connectors, which can be equipped with SFP transceivers to achieve up to four STM-1 or two STM-4 interfaces.

Moreover, the board offers four GbE interfaces towards the backplane, which allows the board to operate in redundant setups as well as to select whether data transfer resides in the AMC Common-Option region (port 0 / 1) or in the Fat-Pipe region (port 4 / 8).

When operating in the Fat-Pipe region, the NAT-AMC-SDH will typically connect to a 10G Ethernet switch (e.g. NAT-MCH) configured to Gigabit transmission mode for the respective port. In addition to the multiple Ethernet interfaces, the NAT-AMC-SDH is prepared for optional Fat Pipe support (i.e. XAUI or SRIO) at AMC ports 4-7.

Equipped with a STRATUM-3 PLL, the NAT-AMC-SDH can derive the network clock from one of the line interface ports and supply a synchronized clock to all other AMCs in the system, or derive the system clock from the AMC backplane connector and supply a synchronized clock to all line interfaces. Alternatively, when set to free-running mode, the PLL can be used to operate the NAT-AMC-SDH as a clock generator.

Besides the payload data, all configuration and management data going to and coming from the NAT-AMC-SDH board is transmitted via Ethernet. Therefore, a control interface within the FPGA is able to handle Ethernet frames carrying a special protocol based upon regular Layer2 Ethernet. This handles memory-mapped accesses on the board internal memory map, covering both FPGA internal blocks as well as external devices like the TEMUX336. This allows the controlling host to reside inside or outside the MTCA system, ideal for distributed applications.

Key Features

- AMC form factor, single mid- or full-size

Add/drop multiplexer, E1/T1 and SDH interfaces

- PMC TEMUX336

- 252 E1or 336 T1 framers

- 4 OC-3/STM-1 or 2 OC-12/STM-4 interfaces

- access possible down to single DS0 level

FPGA

- XLINX Kintex-7: XC7K325T or XC7K160T

- Available for custom use

- Optionally featuring

Memory

Front Panel Elements

- Four SFP connectors to host: either 4x OC-3/STM-1 SFP or 2x OC-12/STM-4 SFP transceivers

- Four bi-color link LEDs

- Standard AMC LEDs

Backplane Connectivity

- 4x Gigabit Ethernet interfaces at AMC ports 0, 1, 4, 8

- optional fat pipe (XAUI or SRIO) at AMC ports 4-7

- ESSI for redundant/failover operation at AMC port 12

iTDM Interface

Operating System Support

- Host driver for Ethernet Control Interface, supported O/S: OK-1, LINUX

Related Products

Order Codes

NAMC-SDH- [Option]

| -1-0-1-1 | single mid-size AMC with non-intelligent add-drop multiplexer for SDH; 1 => Kintex XC7K160 T / 0 = no external memory / 1 => OC3-STM1 / 1 => 1 x STM1 transceiver |

| -0-2-2-1 |

single mid-size AMC with non-intelligent add-drop multiplexer for SDH; 0 => Kintex XC7K325T – 2 => ext. RAM (2 x 72 Mb QDR2 + SRAM) – 2 => STM4 (OC12) – 1 => 1 x STM4 transceiver |

| -1-0-1-2 |

single mid-size AMC with non-intelligent add-drop multiplexer for SDH; 1 => Kintex XC7K160T / 0 => no external memory / 1 => STM1 (OC3) / 2 => 2 x STM1 (OC3) transceivers |

| -1-1-2-1 |

single mid-size AMC with non-intelligent add-drop multiplexer for SDH; 1=>KintexXC7K160 / 1=> one 72Mbit QDR2+SRAM / 2=> STM4 (OC12) transceiver / 1=> one STM4 transceiver |

| -1-0-1-4 |

single mid-size AMC with non-intelligent add-drop multiplexer for SDH; 1 => Kintex XC7K160T / 0 => no external memory / 1 => STM1 (OC3) / 4 => 4 x STM1 (OC3) transceivers |

| -0-2-1-4 |

single mid-size AMC with non-intelligent add-drop multiplexer for SDH; 0 => Kintex XC7K325T // 2 => two 72Mbit QDR2+ SRAMs // 1=> STM1 (OC-3) // 4 => four STM1 transceivers |

NAMC-SDH- [Option F] – [Option M] -[Option S] -[Option N]

| Option | Value | Description |

| F

|

-0 | Kintex-7 FPGA XC7K325T |

| -1 | Kintex-7 FPGA XC7K160T | |

| other types on request

|

||

| M

|

-0 | FPGA external memory: none |

| -1 | FPGA external memory: 1x 72Mbit QDR2+ SRAM | |

| -2

|

FPGA external memory: 2x 72Mbit QDR2+ SRAM

|

|

| S

|

-0 | type of SFP transceiver (SDH level): none |

| -1 | type of SFP transceiver (SDH level): STM1 (OC-3) | |

| -2

|

type of SFP transceiver (SDH level): STM4 (OC-12)

|

|

| N | -0 | no transceiver |

| -1 | one STM1 or STM4 transceiver | |

| -2 | two STM1 or STM4 transceivers | |

| -3 | three STM1 transceivers | |

| -4 | four STM1 transceivers |

Solutions / Applications

- High density multiplexers, multi-service switches, edge routers and digital modems

- Access devices

- SONET/SDH add drop and terminal multiplexers

- Optical access equipment

- Digital access cross-connect systems

- Data monitoring systems

- Network test equipment