NAT-MCH-Gen4 Clock-Module User Manual V1.3

#### **Disclaimer**

The following document, compiled by N.A.T. GmbH (henceforth called N.A.T.), represents the current status of the product's development. The document is updated on a regular basis. Any changes which might ensue, including those necessitated by updated specifications, are considered in the latest version of this documentation. N.A.T. is under no obligation to notify any person, organization, or institution of such changes or to make these changes public in any other way.

This document has been compiled with great care, however the document could still include technical inaccuracies or typographical errors.

N.A.T. offers no warranty, either expressed or implied, for the contents of this documentation or for the product described therein, including but not limited to the warranties of merchantability or the fitness of the product for any specific purpose.

In no event will N.A.T. be liable for any loss of data or for errors in data utilization or processing resulting from the use of this product or the documentation. In particular, N.A.T. will not be responsible for any direct or indirect damages (including lost profits, lost savings, delays or interruptions in the flow of business activities, including but not limited to, special, incidental, consequential, or other similar damages) arising out of the use of or inability to use this product or the associated documentation, even if N.A.T. or any authorized N.A.T. representative has been advised of the possibility of such damages.

The use of registered names, trademarks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations (patent laws, trade mark laws, etc.) and therefore free for general use. In no case does N.A.T. guarantee that the information given in this document is free of such third-party rights.

Neither this document nor any part thereof may be copied, translated, or reduced to any electronic medium or machine form without the prior written consent from N.A.T. GmbH.

This product (and the associated documentation) is governed by the N.A.T. General Conditions and Terms of Delivery and Payment.

#### Note:

The release of the User Manual is related to a certain HW board revision. For HW revisions earlier than the one given chapter "Supported HW Revisions" please contact N.A.T. for the corresponding older Manual release.

## **Table of Contents**

| 1 | INTR  | ODUCTION                               | 6  |

|---|-------|----------------------------------------|----|

|   | 1.1   | FUNCTIONAL OVERVIEW                    | 6  |

|   | 1.2   | INPUT CLOCK SIGNALS                    | 7  |

|   | 1.3   | OUTPUT CLOCK SIGNALS                   | 7  |

| 2 | CONF  | FIGURATION - OVERVIEW                  | 8  |

|   | 2.1   | CLOCK ROUTING                          | 8  |

|   | 2.1.1 | Exclusive Connections                  | 9  |

|   | 2.2   | PLL CONFIGURATION                      | 9  |

|   | 2.2   | .1.1 Setting the PLL Reference Input   | 9  |

|   | 2.2   | .1.2 Set the Reference Input Frequency | 10 |

|   | 2.2   | .1.3 Set the reference input priority  | 10 |

|   | 2.2   | .1.4 Configure a PLL output            | 10 |

|   | 2.2   | .1.5 Enable the PLL                    | 11 |

|   | 2.2.2 | Setting the Front I/O AC/DC Coupling   | 11 |

| 3 | CLI / | SCRIPT BASED CLOCK CONFIGURATION       | 12 |

|   | 3.1   | Examples:                              | 12 |

|   | 3.1.1 | Basic Routing Example                  | 12 |

|   | 3.1.2 | Multi-Endpoint Example                 | 12 |

|   | 3.1.3 | Complex Routing Example with PLL       | 13 |

| 4 | ІРМІ  | BASED CONTROL CONFIGURATION:           | 14 |

## List of Tables

| Table 1: List of used abbreviations            | 5  |

|------------------------------------------------|----|

| Table 2: Routing Limitations                   | 9  |

| Table 3: Possible PLL Reference Inputs         | 9  |

| Table 4: PLL Outputs                           | 10 |

| Table 5: AC/DC Coupling                        | 11 |

| Table 6: Clock IPMI Commands                   | 14 |

| Table 7: Set Clock Route Command               | 14 |

| Table 8: Set Clock Configuration Command       | 14 |

| Table 9: Configuration Nodes                   | 15 |

| Table 10: Configuration Items                  | 16 |

| Table 11: Input / Output Frequency Assignments | 16 |

# List of Figures

Es konnten keine Einträge für ein Abbildungsverzeichnis gefunden werden.

## Conventions

If not specified otherwise, addresses and memory maps are provided in hexadecimal notation, identified by 0x. Table 1 lists the abbreviations used in this document:

Table 1: List of used abbreviations

| Abbreviation     | Description                                        |  |

|------------------|----------------------------------------------------|--|

| AMC              | Advanced Mezzanine Card                            |  |

| ATCA             | Advanced Telecommunications Computing Architecture |  |

| CRC              | Cyclic Redundancy Check                            |  |

| DIP SW           | Dual In-Line Switch                                |  |

| EEPROM           | Electrically Erasable PROM                         |  |

| FPGA             | Field Programmable Gate Array                      |  |

| GbE              | Gigabit Ethernet                                   |  |

| HS               | Hot Swap                                           |  |

| I <sup>2</sup> C | Inter-Integrated Circuit                           |  |

| 1/0              | Input/Output                                       |  |

| IP               | Internet Protocol                                  |  |

| IPMB             | Intelligent Platform Management Bus                |  |

| IPMI             | Intelligent Platform Management Interface          |  |

| JTAG             | Joint Test Action Group                            |  |

| μС               | Microcontroller                                    |  |

| μΤСΑ             | Micro Telecommunications Computing Architecture    |  |

| MUX              | Multiplexer                                        |  |

| PCB              | Printed Circuit Board                              |  |

| PCI(e)           | Peripheral Component Interconnect (Express)        |  |

| Rx               | Receiver                                           |  |

| RAM              | Random Access Memory                               |  |

| (P)ROM           | (Programmable) Read Only Memory                    |  |

| PLL              | Phase Locked Loop                                  |  |

| SFP              | Small Form-Factor Pluggable                        |  |

| TCKL             | Telecom Clock                                      |  |

## 1 Introduction

#### 1.1 Functional Overview

The NAT-MCH-G4-CLK is a mezzanine module for the NAT-MCH-G4 MCH supporting telecom clocks TCLKA and TCLKB as well as a 100Mhz FCLKA for PCIe modules. The module provides support for manipulating the various input clocks and routing of the clocks to the desired outputs. To allow a flexible interconnect, the module is equipped with two crosspoint switches and a local PLL. The output of either a local oscillator or an oven controlled oscillator can be used as a reference input to the PLL.

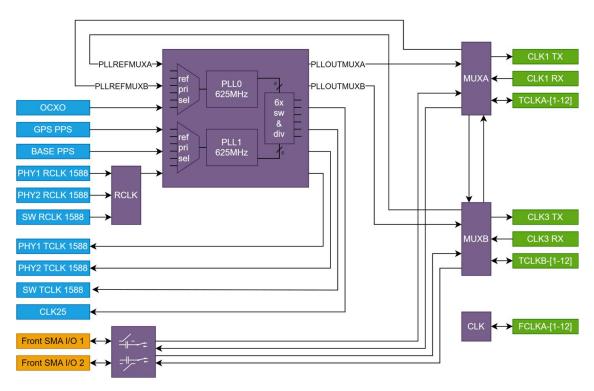

Figure 1: MCH-G4 Clock Module Blockdiagram

Figure 1 shows an overview of the clock module and possible interconnects. The inputs and outputs of the clock module shown in blue are located on the connector to the MCH base module. The front panel SMA connections are shown in orange. The backplane connections are shown in green. Everything that illustrates the internal functionality is coloured in purple.

The PLL system consists of PLL0 and PLL1 and has 6 reference inputs and 6 outputs. For each PLL (0 and 1) a reference priority list is configurable. A source PLL can be selected for each of the 6 outputs. Furthermore, the fixed PLL frequency of 500 MHz can be changed for each output via an adjustable frequency divider.

Front I/O signals can be switched between input and output and AC or DC coupling.

#### 1.2 INPUT CLOCK SIGNALS

The clock module receives its input from the following clock sources:

- Front I/O coax connector at the front panel of the MCH (\*)

- IEEE1588 reference clock input which is recovered from either the Ethernet PHYs or the Ethernet switch located on the base board

- TCLKB as coming from the backplane (\*\*)

- CLK1\_RX, CLK3\_RX as coming from the backplane

- GPS 1pps signal

Both front I/O signal can be switched between Input/Output and AC/DC coupling.

#### 1.3 OUTPUT CLOCK SIGNALS

Depending on the type of clock signal, the input clock signal can either be connected directly to one of the output signals or being routed through the onboard PLL and then connected to one of the output signals. Possible connections will be detailed in chapter 2.1. The module can provide the following output signals:

- Front I/O to coax connector located at the front panel (\*)

- IEEE1588 synchronized output clocks

- TCLKA Backplane Telecom Clock A (\*\*\*)

- FCLKA Backplane Fabric Clock A a 100Mhz reference clock for PCIe applications. This clock is always on and can't be configured

- CLK1\_TX, CLK3\_TX backplane clocks

- \* Both front I/O signal can be switched between Input/Output and AC or DC coupling.

- \*\* TCLKB usually is the backplane clock input to the MCH. On the MCH Gen4 this clock can be configured as output to the AMCs as well. Users who want to make usage of this option should take care of possible termination issues.

- \*\*\* TCLKA usually is the backplane clock output from the MCH. On the MCH Gen4 this clock can be configured as clock input to the MCH as well. Users who want to make usage of this option should take care of possible termination issues.

-7-

### 2 CONFIGURATION - OVERVIEW

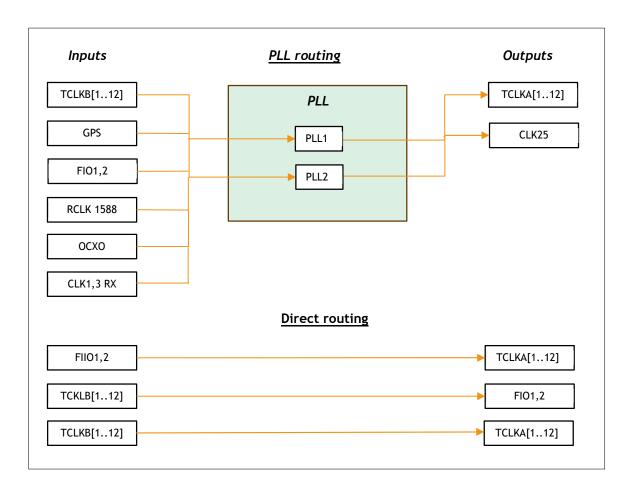

In its basic operation the clock module builds a connection between an input clock and one or multiple output clocks. The input signal can either be directly connected to one of the outputs or being routed through the onboard PLL. The purpose of the onboard PPL is to stabilize and convert the input clock signal into an output clock signal. I.e. convert a 1pps input clock signal to a 10MHz output clock signal.

All type of clock signals can be configured individually.

The table in Appendix A gives an overview about the various input and output signals as well as internally generated signals by the onboard devices. For the ease of addressing or configuration of these signals they are named "nodes" in the following chapters.

Each node has been assigned a symbolic name and an ID for addressing these nodes by the MCH CLI or by IPMI commands.

#### 2.1 CLOCK ROUTING

The connection diagram below shows all possible clock interconnects:

Please note that multiple connections are possible, for example a TCLKB input can be routed to the PLL and in parallel to the front I/O connector FIO2. But the connection matrix is not completely orthogonal, limitations arise from internal resources. Table 2 gives an overview about the limitations.

#### 2.1.1 Exclusive Connections

The following table shows the internal routing limitations. The routing between certain inputs nodes and certain output nodes is limited to one exclusive connection:

Table 2: Routing Limitations

| Input Nodes | Constraint | Output Nodes           |

|-------------|------------|------------------------|

| PHY1_1588   | One of     | PLLO, PLL1             |

| PHY2_1588   |            |                        |

| SW_1588     |            |                        |

| FIO1        | One of     | PLLO, PLL1             |

| CK1_RX      |            |                        |

| FIO2        | One of     | PLLO, PLL1, TCKLA[112] |

| CLK2_RX     |            |                        |

| TCKLB[112]  |            |                        |

|             |            |                        |

An attempt to route multiple connections between those nodes leads to an error code being returned.

#### 2.2 PLL CONFIGURATION

The PLL block of the MCH clock module has two independent PLLs (PLL0, PLL1). Each of the PLLs can be configured individually. The recommended PLL configuration sequence is outlined below:

- 1. Apply a routing between input clocks and one of the PLLs

- 2. Apply a routing between a PLL and one of the output clocks

- 3. Set the reference input frequency (optional, depending on input)

- 4. Set the reference priority

- 5. Set the output frequency

- 6. Enable the PLL

The configuration nodes within the can be found in Appendix A.

#### 2.2.1.1 Setting the PLL Reference Input

The reference inputs are common for both PLLs. Each PLL can be assigned one or multiple reference inputs. The following table lists the input signals that can be used as refence inputs to the PLLs. can be set. Furthermore, it is not necessary to set the frequency for inputs with a fixed function, as the correct frequency is already set automatically at system startup (marked with \*).

To set a reference input use a routing command to route the desired input to one of the PLLs.

Table 3: Possible PLL Reference Inputs

| Input      | Description                         |

|------------|-------------------------------------|

| FIO1       | Front Coax Connector Input/Output 1 |

| FIO2       | Front Coax Connector Input/Output 2 |

| PHY1_1588* | IEEE1588 reference input from Phy1  |

| PHY2_1588* | IEEE1588 reference input from Phy2  |

| SW_1588* | IEEE1588 reference input from ethernet switch       |

|----------|-----------------------------------------------------|

| GPS_PPS* | 1 pps signal from GPS receiver                      |

| OCXO*    | Reference frequency from Oven Controlled Oscillator |

| BP_CLK1  | Reference clock from backplane signal RX_CLK1 (*)   |

| BP_CLK3  | Reference clock from backplane signal RX_CLK3 (*)   |

<sup>(\*)</sup> requires setting of reference frequency - see below

### 2.2.1.2 Set the Reference Input Frequency

The expected input frequency must be set for the references used.

The following table shows the predefined frequencies

Valid Frequencies in Hz to be set are 1, 10, 25, 100, 250, 500, 1k, 10k, 25k, 50k, 100k, 250k, 500k 1M, 10M, 25M, 50M and 100M.

PLLs are getting disabled when the reference frequency input settings is changed.

#### 2.2.1.3 Set the reference input priority

If multiple input signals are routed to the PLL, the PLL can automatically switch between the input signals according to the priority assigned to the input signals. I.e. if the signal with highest priority becomes instable or disappears, the PLL automatically switches to the signal with the second highest priority and so on.

Priority 0 is the highest and the default. A value of 15 disables the reference input. If a reference input frequency fails, which can be detected as the expected frequency was previously configured, the system automatically switches to the input with the next highest priority.

#### 2.2.1.4 Configure a PLL output

The configuration of the PLL outputs includes the setting of a desired output frequency and the selection of which PLL (0/1) of the PLL system serves as the source for the respective output. Table 4 lists all signals that are PLL outputs and can therefore be configured as described.

Table 4: PLL Outputs

| Signal         | Description                  |

|----------------|------------------------------|

| PHY1_TCLK_1588 | 1588 Clock to Uplink 1 PHY   |

| PHY2_TCLK_1588 | 1588 Clock to Uplink 2 PHY   |

| SW_TCLK_1588   | 1588 Clock to Base Switch    |

| CLK25          | 1588 synchronous 25MHz Clock |

| FIO1           | Output to Coax Front I/O 1   |

| FIO2           | Output to Coax Front I/O 2   |

| TCLKA1-12      | Telecom Clock A to AMCs      |

| TCLKB1-12      | TCLKB Inputs from AMCs       |

The valid Frequencies are listed in Appendix A.

Version 1.3 -10-

#### 2.2.1.5 Enable the PLL

When the PLL system is fully configured for the desired use, the individual PLLs (1/2) can be activated.

#### 2.2.2 Setting the Front I/O AC/DC Coupling

The Front I/O interface can be configured for AC or DC coupling. Possible configuration items are:

Table 5: AC/DC Coupling

| Conf. Item | Coupling | Applicable<br>Nodes |

|------------|----------|---------------------|

| FIO_AC     | AC       | FIO1, FIO2          |

| FIO_DC     | DC       | FIO1, FIO2          |

The default mode after power up is DC coupling!

#### 2.2.3 Resetting the Clock Configuration

The complete clock configuration can be set into the initial state after power up with the RESET command.

Table 6: Configuration reset

| Conf. Item | Applicable<br>Nodes |

|------------|---------------------|

| RESET      | GEN                 |

Version 1.3 -11-

### 3 CLI / SCRIPT BASED CLOCK CONFIGURATION

The configuration of the clock module is supported through the command line interface (CLI) of the MCH. To configure the clock module either individual commands can be entered at the MCH's console or a complete set of configuration commands can be provided to the clock module by the MCH's script functionality.

The basic syntax of the CLI commands for clock routing and configuration are:

Set clock route [site] [src\_node] [dst\_node]

Set clock route [site] [src\_node] [fst\_node] [lst\_node]

Set clock config [site] [node] [config\_item] [value]

[site] = 1 or 2 for MCH1 or MCH2

[node] = clock signal symbols according to Appendix A.

[config\_item] = clock configuration items according to Appendix A.

[value] = to configure the Priority this are values in the range 0-15

a frequency is configured by using the frequency IDs according

to Appendix A

#### 3.1 EXAMPLES:

### 3.1.1 Basic Routing Example

Establish a clock routing on the clock module of MCH1 and route the input clock (TCLKB3) from AMC3 to the TCLKA5 output for AMC5:

Set clock route 1 TCLKB3 TCLKA5

#### 3.1.2 Multi-Endpoint Example

Route the Front I/O signal 1 (FIO1) to all TCLKA outputs:

Set clock route 1 FIO1 TCLKA1 TCLKA12

#### 3.1.3 Complex Routing Example with PLL

- Route the Front I/O signal 1 (FIO1) to PLLO and PLL2.

- Verify that the input frequency is 25MHz (ID=17).

- Connect the PLLO output to the TCLKA signals and the PLL1 output to the TCLKB signals.

- Set the output frequency for TCLKA to 50MHz(ID=18) and TCLKB frequency to 1Hz(ID=1).

- Enable both PLLs

```

set clock route 1 FIO1 PLL0_REF

set clock route 1 FIO1 PLL1_REF

set clock route 1 PLL0_OUT TCLKA1 TCLKA12

set clock route 1 PLL1_OUT TCLKB1 TCLKB12

set clock config 1 FIO1 PLL_REF_FREQ 17

set clock config 1 FIO1 PLL0_REF_PRIO 0

set clock config 1 FIO1 PLL1_REF_PRIO 0

set clock config 1 TCLKA1 PLL1_OUT_FREQ 18

set clock config 1 TCLKB1 PLL_OUT_FREQ 1

set clock config 1 PLL0_OUT PLL_EN

set clock config 1 PLL1_OUT PLL_EN

```

#### 3.1.4 Configuration Reset Example

set clock config 1 GEN RESET

## 4 IPMI BASED CONTROL CONFIGURATION:

All IPMI configuration commands send to the clock module are using an extension of the IPMI\_NETFN\_CONTRO\_REQ command. The IPMI interface uses the same commands, configuration items and values as the CLI. The following commands are supported:

Table 6: Clock IPMI Commands

| #    | Command Description                   | Identifier         | Value |

|------|---------------------------------------|--------------------|-------|

| 0x20 | Set routing between a clock input and | IPMI_CMD_CLK_ROUTE | 0x1A  |

|      | output                                |                    |       |

| 0x21 | Set clock configuration               | IPMI_CMD_CLK_CONF  | 0x1B  |

Table 7: Set Clock Route Command

| Request |

|---------|

|---------|

| Byte | Field description                                                 |

|------|-------------------------------------------------------------------|

| 1    | PICMG®-defined group extension command - 0x00                     |

|      | Control information                                               |

|      | [71] – unused                                                     |

| 2    | 0: on / off control                                               |

|      | 1b = switch route on                                              |

|      | 0b = switch route off                                             |

| 3    | Clock Input ID:                                                   |

| 3    | Rever to Appendix A for valid Clock Node IDs                      |

|      | Clock output ID                                                   |

| 4    | ID of a single output clock or the first clock of a clock range   |

|      | Rever to Appendix A for valid Clock Node IDs                      |

| (5)  | Clock output ID – optional - used for clock range definition only |

| (5)  | Last Clock ID to be configured                                    |

| 1    | Completion Code                                                   |

Response

Table 8: Set Clock Configuration Command

Request

| Byte | Field description                             |  |  |

|------|-----------------------------------------------|--|--|

| 1    | PICMG®-defined group extension command - 0x00 |  |  |

| 2    | Clock ID                                      |  |  |

| 3    | Node ID – refer to Appendix A                 |  |  |

| 4    | Config_item – refer to Appendix A             |  |  |

| 5    | Value – a configuration value - optional      |  |  |

| 1    | Completion Code                               |  |  |

Response

Version 1.3 -14-

# Appendix A: Configuration Nodes and Items

Table 9: Configuration Nodes

| Output Nodes           TCLKA[112]         Telecom Clock A to AMCs (*)         [0x010x0c]           TCLKC[112]         Telecom Clock C to AMCs (*) (**)         [0x210x2c]           FCLKA[112]         Fabric Clock A to AMCs         [0x310x3c]           FCLKA[112]         Fabric Clock A to AMCs         [0x310x3c]           SW_TCLK1588         1588 Clock to Base Switch         0x40           PHY1_TCLK1588         1588 Clock to Uplink 1 PHY         0x41           PHY2_TCLK1588         1588 Clock to Uplink 2 PHY         0x42           CLK25_1588         1588 Synchronous 25MHz Clock         0x43           CLK1_TX         Backplane clock TX1         0x46           CLK3_TX         Backplane clock TX3         0x47           Input Nodes           TCLKB Inputs from AMCs (***)         [0x110x1c]           MCLK         Local 49.152 MHz Oscillator         0x50           GPS         PPS Signal generated by onboard GPS module         0x51           OCXO         Oven controlled oscillator located on the base         0x52           MCH         SW_PPS         1 pps clock generated by the Base Switch         0x53           SW_RX1588         Recovered IEEE1588 clock from Uplink 1 PHY         0x55           PHY1_RX15                                                                    | Symbol         | Description                                | NodelD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| TCLKA[112]         Telecom Clock A to AMCs (*)         [0x010x0c]           TCLKC[112]         Telecom Clock C to AMCs (*) (**)         [0x210x2c]           FCLKA[112         Fabric Clock A to AMCs         [0x310x3c]           SW_TCLK1588         1588 Clock to Base Switch         0x40           PHY1_TCLK1588         1588 Clock to Uplink 1 PHY         0x41           PHY2_TCLK1588         1588 Clock to Uplink 2 PHY         0x42           CLK25_1588         1588 synchronous 25MHz Clock         0x43           CLK1_TX         Backplane clock TX1         0x46           CLX3_TX         Backplane clock TX3         0x47           Input Nodes         Input Nodes           TCLKB[112]         TCLKB Inputs from AMCs (***)         [0x110x1c]           MCLK         Local 49.152 MHz Oscillator         0x50           GPS         PPS Signal generated by onboard GPS module         0x51           OCXO         Oven controlled oscillator located on the base         0x52           MCH         SW_PPS         1 pps clock generated by the Base Switch         0x53           SW_RX1588         Recovered IEEE1588 clock from base switch         0x54           PHY1_RX1588         Recovered IEEE1588 Clock from Uplink 1 PHY         0x56           CLK1_RX         B                               | ,              |                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| TCLKC[112]         Telecom Clock C to AMCs (*) (**)         [0x210x2c]           FCLKA[112]         Fabric Clock A to AMCs         [0x310x3c]           SW_TCLK1588         1588 Clock to Base Switch         0x40           PHY1_TCLK1588         1588 Clock to Uplink 1 PHY         0x41           PHY2_TCLK1588         1588 Slock to Uplink 2 PHY         0x42           CLK25_1588         1588 synchronous 25MHz Clock         0x43           CLK1_TX         Backplane clock TX1         0x46           CLK3_TX         Backplane clock TX3         0x47           Input Nodes           TCLKB Inputs from AMCs (***)         [0x110x1c]           MCLK         Local 49.152 MHz Oscillator         0x50           GPS         PPS Signal generated by onboard GPS module         0x50           GPS         PPS Signal generated by onboard GPS module         0x51           OCXO         Oven controlled oscillator located on the base         0x52           MCH         0x52         MCH           SW_PPS         1 pps clock generated by the Base Switch         0x53           SW_RX1588         Recovered IEEE1588 Clock from Uplink 1 PHY         0x55           PHY2_RX1588         Recovered IEEE1588 Clock from Uplink 2 PHY         0x56 <td< td=""><td>TCLKA[112]</td><td>,</td><td>[0x010x0c]</td></td<> | TCLKA[112]     | ,                                          | [0x010x0c]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| SW_TCLK1588         1588 Clock to Base Switch         0x40           PHY1_TCLK1588         1588 Clock to Uplink 1 PHY         0x41           PHY2_TCLK1588         1588 Clock to Uplink 2 PHY         0x42           CLK25_1588         1588 synchronous 25MHz Clock         0x43           CLK1_TX         Backplane clock TX1         0x46           CLK3_TX         Backplane clock TX3         0x47           Input Nodes           TCLKB Inputs from AMCs (***)         [0x110x1c]           MCLK         Local 49.152 MHz Oscillator         0x50           GPS         PPS Signal generated by onboard GPS module         0x51           OCXO         Oven controlled oscillator located on the base MCH         0x52           SW_PS         1 pps clock generated by the Base Switch         0x53           SW_RX1588         Recovered IEEE1588 clock from base switch         0x54           PHY1_RX1588         Recovered IEEE1588 Clock from Uplink 1 PHY         0x55           PHY2_RX1588         Recovered IEEE1588 Clock from Uplink 2 PHY         0x56           CLK1_RX         Backplane clock RX1         0x57           CLK3_RX         Backplane clock RX3         0x58           Bi-Directional Nodes           FIO1         Clock Input/Output at F                                                    |                | ` '                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| PHY1_TCLK1588         1588 Clock to Uplink 1 PHY         0x41           PHY2_TCLK1588         1588 Clock to Uplink 2 PHY         0x42           CLK25_1588         1588 synchronous 25MHz Clock         0x43           CLK1_TX         Backplane clock TX1         0x46           CLK3_TX         Backplane clock TX3         0x47           Input Nodes           TCLKB Inputs from AMCs (***)         [0x110x1c]           MCLK         Local 49.152 MHz Oscillator         0x50           GPS         PPS Signal generated by onboard GPS module         0x51           OCXO         Oven controlled oscillator located on the base MCH         0x52           SW_PPS         1 pps clock generated by the Base Switch         0x53           SW_RX1588         Recovered IEEE1588 clock from base switch         0x54           PHY1_RX1588         Recovered IEEE1588 Clock from Uplink 1 PHY         0x55           PHY2_RX1588         Recovered IEEE1588 Clock from Uplink 2 PHY         0x56           CLK1_RX         Backplane clock RX1         0x57           CLK3_RX         Backplane clock RX3         0x58           Bi-Directional Nodes           FIO1         Clock Input/Output at Front Coax I/O 1         0x44           FIO2         Clock Input/Outp                                                    | FCLKA[112      | Fabric Clock A to AMCs                     | [0x310x3c]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| PHY2_TCLK1588   1588 Clock to Uplink 2 PHY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SW_TCLK1588    | 1588 Clock to Base Switch                  | 0x40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| CLK25_1588                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | PHY1_TCLK1588  | 1588 Clock to Uplink 1 PHY                 | 0x41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| CLK25_1588                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | PHY2_TCLK1588  | 1588 Clock to Uplink 2 PHY                 | 0x42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| CLK3_TX Backplane clock TX3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CLK25_1588     |                                            | 0x43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| Input Nodes  TCLKB[112] TCLKB Inputs from AMCs (***) [0x110x1c]  MCLK Local 49.152 MHz Oscillator 0x50  GPS PPS Signal generated by onboard GPS module 0x51  OCXO Oven controlled oscillator located on the base MCH  SW_PPS 1 pps clock generated by the Base Switch 0x53  SW_RX1588 Recovered IEEE1588 clock from base switch 0x54  PHY1_RX1588 Recovered IEEE1588 Clock from Uplink 1 PHY 0x55  PHY2_RX1588 Recovered IEEE1588 Clock from Uplink 2 PHY 0x56  CLK1_RX Backplane clock RX1 0x57  CLK3_RX Backplane clock RX3 0x58  Bi-Directional Nodes  FIO1 Clock Input/Output at Front Coax I/O 1 0x44  FIO2 Clock Input/Output at Front Coax I/O 2 0x45  Internal Nodes  PLL0_REF PLL0 input node 0x61  PLL1_REF PLL1 input node 0x70  PLL1_OUT PLL1 output node 0x71  Generic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | CLK1_TX        | Backplane clock TX1                        | 0x46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| TCLKB Inputs from AMCs (***) [0x110x1c]  MCLK Local 49.152 MHz Oscillator 0x50  GPS PPS Signal generated by onboard GPS module 0x51  OCXO Oven controlled oscillator located on the base MCH  SW_PPS 1 pps clock generated by the Base Switch 0x53  SW_RX1588 Recovered IEEE1588 clock from base switch 0x54  PHY1_RX1588 Recovered IEEE1588 Clock from Uplink 1 PHY 0x55  PHY2_RX1588 Recovered IEEE1588 Clock from Uplink 2 PHY 0x56  CLK1_RX Backplane clock RX1 0x57  CLK3_RX Backplane clock RX3 0x58  Bi-Directional Nodes  FIO1 Clock Input/Output at Front Coax I/O 1 0x44  FIO2 Clock Input/Output at Front Coax I/O 2 0x45  Internal Nodes  PLL0_REF PLL0 input node 0x61  PLL1_REF PLL1 input node 0x70  PLL1_OUT PLL1 output node 0x71  Generic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CLK3_TX        | Backplane clock TX3                        | 0x47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| MCLK Local 49.152 MHz Oscillator 0x50 GPS PPS Signal generated by onboard GPS module 0x51 OCXO Oven controlled oscillator located on the base MCH  SW_PPS 1 pps clock generated by the Base Switch 0x53 SW_RX1588 Recovered IEEE1588 clock from base switch 0x54 PHY1_RX1588 Recovered IEEE1588 Clock from Uplink 1 PHY 0x55 PHY2_RX1588 Recovered IEEE1588 Clock from Uplink 2 PHY 0x56 CLK1_RX Backplane clock RX1 0x57 CLK3_RX Backplane clock RX3 0x58  Bi-Directional Nodes  FIO1 Clock Input/Output at Front Coax I/O 1 0x44 FIO2 Clock Input/Output at Front Coax I/O 2 0x45  Internal Nodes  PLL0_REF PLL0 input node 0x60 PLL0_OUT PLL0 output node 0x70 PLL1_REF PLL1 input node  Ox70 PLL1_OUT PLL1 output node  Generic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                |                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| GPS PPS Signal generated by onboard GPS module 0x51  OCXO Oven controlled oscillator located on the base MCH  SW_PPS 1 pps clock generated by the Base Switch 0x53  SW_RX1588 Recovered IEEE1588 clock from base switch 0x54  PHY1_RX1588 Recovered IEEE1588 Clock from Uplink 1 PHY 0x55  PHY2_RX1588 Recovered IEEE1588 Clock from Uplink 2 PHY 0x56  CLK1_RX Backplane clock RX1 0x57  CLK3_RX Backplane clock RX3 0x58  Bi-Directional Nodes  FIO1 Clock Input/Output at Front Coax I/O 1 0x44  FIO2 Clock Input/Output at Front Coax I/O 2 0x45  Internal Nodes  PLL0_REF PLL0 input node 0x60  PLL0_OUT PLL0 output node 0x70  PLL1_OUT PLL1 output node  Generic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | TCLKB[112]     | TCLKB Inputs from AMCs (***)               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| OCXO Oven controlled oscillator located on the base MCH  SW_PPS 1 pps clock generated by the Base Switch Ox53  SW_RX1588 Recovered IEEE1588 clock from base switch Ox54  PHY1_RX1588 Recovered IEEE1588 Clock from Uplink 1 PHY Ox55  PHY2_RX1588 Recovered IEEE1588 Clock from Uplink 2 PHY Ox56  CLK1_RX Backplane clock RX1 Ox57  CLK3_RX Backplane clock RX3 Ox58  Bi-Directional Nodes  FIO1 Clock Input/Output at Front Coax I/O 1 Ox44  FIO2 Clock Input/Output at Front Coax I/O 2 Ox45  Internal Nodes  PLL0_REF PLL0 input node Ox60  PLL0_OUT PLL0 output node Ox70  PLL1_OUT PLL1 output node Ox71  Generic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | MCLK           | Local 49.152 MHz Oscillator                | 0x50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| MCH  SW_PPS 1 pps clock generated by the Base Switch 0x53  SW_RX1588 Recovered IEEE1588 clock from base switch 0x54  PHY1_RX1588 Recovered IEEE1588 Clock from Uplink 1 PHY 0x55  PHY2_RX1588 Recovered IEEE1588 Clock from Uplink 2 PHY 0x56  CLK1_RX Backplane clock RX1 0x57  CLK3_RX Backplane clock RX3 0x58  Bi-Directional Nodes  FIO1 Clock Input/Output at Front Coax I/O 1 0x44  FIO2 Clock Input/Output at Front Coax I/O 2 0x45  Internal Nodes  PLL0_REF PLL0 input node 0x60  PLL0_OUT PLL0 output node 0x61  PLL1_REF PLL1 input node 0x70  PLL1_OUT PLL1 output node 0x71  Generic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | GPS            | PPS Signal generated by onboard GPS module | 0x51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |